- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-FIR (Altera)IP FIR COMPILER

�� �

�

�

�4–8�

�Chapter� 4:� Functional� Description�

�FIR� Compiler�

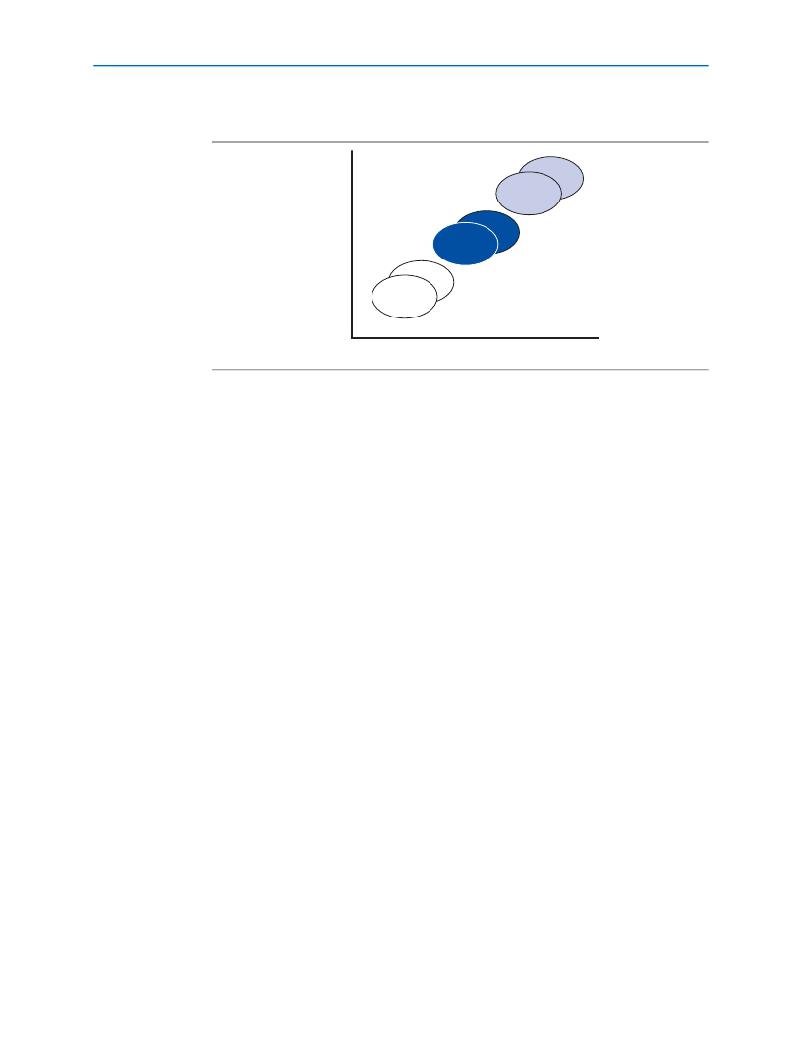

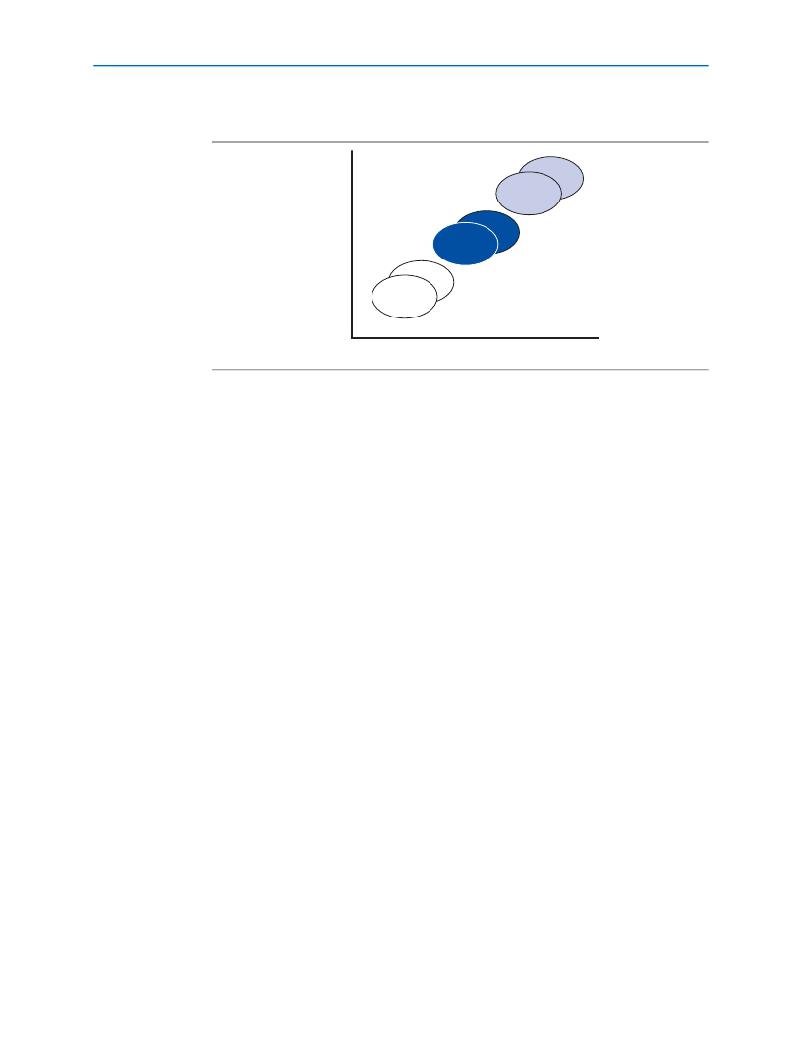

��Figure� 4–6.� Fixed� FIR� Filters:� Area� Vs.� Throughput�

�Parallel�

�With� Extended�

�Pipelining�

�Throughput�

�Multi-Bit�

�Serial�

�With� Extended�

�Pipelining�

�Serial�

�With� Extended�

�Pipelining�

�Area�

�Two� serial� filters� operating� in� parallel� compute� the� result� at� twice� the� rate� of� a� single�

�serial� filter.� Three� serial� filters� operate� at� triple� the� speed;� four� operate� at� four� times�

�the� speed.� For� example,� a� 16-bit� serial� FIR� filter� requires� 16� clock� cycles� to� complete� a�

�single� FIR� calculation.� A� multibit� serial� FIR� filter� with� two� serial� structures� takes� only�

�eight� clock� cycles� to� compute� the� result.� Using� four� serial� structures,� only� four� clock�

�cycles� are� required� to� perform� the� computation.� Three� serial� structures� cannot� be� used�

�for� a� 16-bit� serial� structure,� however,� because� 16� does� not� divide� evenly� by� three.�

�Multichannel� Structures�

�When� designing� DSP� systems,� you� may� need� to� generate� two� FIR� filters� that� have� the�

�same� coefficients.� If� high� speed� is� not� required,� your� design� can� share� one� filter,� which�

�uses� fewer� resources� than� two� individual� filters.� For� example,� a� two-channel� parallel�

�filter� requires� two� clock� cycles� to� calculate� two� outputs.� The� resulting� hardware�

�would� need� to� run� at� twice� the� data� rate� of� an� individual� filter.�

�1�

�To� minimize� the� number� of� logic� elements,� use� a� distributed� serial� arithmetic�

�architecture,� multiple� channels,� and� memory� blocks� for� data� and� coefficient� storage.�

�Interpolation� and� Decimation�

�You� can� use� the� FIR� Compiler� to� interpolate� or� decimate� a� signal.� Interpolation�

�generates� extra� points� in� between� the� original� samples;� decimation� removes�

�redundant� data� points.� Both� operations� change� the� effective� sample� rate� of� a� signal.�

�1�

��The� outputs� from� interpolating� and� decimating� filters� that� have� the� same� input� data�

�are� likely� to� be� different.� This� difference� is� because� changing� the� delay� between� the�

�reset� signal� and� the� first� non-zero� input� data� sample� may� make� the� input� sample� go�

�down� a� different� path� of� the� polyphase� filter.� This� means� that� the� input� data� is�

�multiplied� by� a� different� set� of� coefficients� and� the� filter� results� are� different.�

�?� May� 2011� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-NCO

IP NCO COMPILER

IP-NIOS

IP NIOS II MEGACORE

IP-PCI/MT64

IP PCI 64BIT MASTER/TARGET

IP-PCIE/8

IP PCI EXPRESS, X8

IP-POSPHY4

IP POS-PHY L4

IP-RIOPHY

IP RAPID I/O

IP-RLDRAMII

IP RLDRAM II CONTROLLER

IP-RSDEC

IP REED-SOLOMON DECODER

相关代理商/技术参数

IP-FIRII

功能描述:开发软件 FIR Compiler II MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPFLBPT2

制造商:Carlo Gavazzi 功能描述:IL 35MM MUSH P-P PL 22MM RED

IPG1-0-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-41-203-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-51-103-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 10A 65VDC

IPG1-1-52-303-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 30A 65VDC

IPG1-1-61-153-00-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A

IPG1-1-61-153-90-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A